# JASPER

# COM-Based SBC with Integrated Data Acquisition

# Featuring COM Express Type 6 Compact / Basic COMs

**User Manual**

Revision 2.2

Diamond Systems Corporation Sunnyvale, CA 94086 USA © 2025 Diamond Systems, Corp. All rights reserved. Diamond Systems logo is a trademark of Diamond Systems, Corp. Technical Support Request Form Tel: 1-650-810-2500 Revision 2.2

# Contents

| 1. | Introduction |                                 |    |

|----|--------------|---------------------------------|----|

|    | 1.1.         | Jasper Product Overview         | 7  |

|    | 1.2.         | Processor Options               | 8  |

|    | 1.3.         | Baseboard Variants              | 9  |

|    | 1.4.         | Jasper Ordering Guide           | 10 |

|    | 1.5.         | Product Photos                  | 11 |

| 2. | Featu        | re List                         | 12 |

| 3. | Block        | Diagrams                        | 14 |

| 4. | Produ        | ct Photos                       | 16 |

| 5. | Functi       | ional Overview                  | 18 |

|    | 5.1.         | COM Express Carrier Board       | 18 |

|    | 5.2.         | Power Supply Specifications     | 18 |

|    | 5.3.         | Ethernet Ports                  | 18 |

|    | 5.4.         | PCIe Link Routing               | 18 |

|    | 5.5.         | SATA M.2 Socket                 | 19 |

|    | 5.6.         | USB                             | 19 |

|    | 5.7.         | Audio                           | 20 |

|    | 5.8.         | LVDS LCD                        | 20 |

|    | 5.9.         | HDMI                            | 20 |

|    | 5.10.        | Serial Ports                    | 20 |

|    | 5.11.        | Data Acquisition                | 20 |

|    | 5.12.        | Backup Battery                  | 20 |

|    | 5.13.        | Trusted Platform Module         | 20 |

|    | 5.14.        | Utility                         | 20 |

|    | 5.15.        | GPIO Header                     | 21 |

|    | 5.16.        | Minicard Socket                 | 21 |

|    | 5.17.        | PCle104 Expansion               | 21 |

|    | 5.18.        | LED Indicators                  | 21 |

| 6. | Data A       | Acquisition Circuit             | 23 |

|    | 6.1.         | Overview                        | 23 |

|    | 6.2.         | FPGA                            | 23 |

|    | 6.3.         | Bus Interface                   | 24 |

|    | 6.4.         | Interrupts                      | 24 |

| 7. | A/D C        | ircuit                          | 26 |

|    | 7.1.         | A/D Input Ranges and Resolution | 26 |

|    | 7.2.         | Unipolar and Bipolar Inputs     | 26 |

|    | 7.3.         | Ranges and Resolutions          | 26 |

|    |              | 7.3.1. Conversion Formulas      | 27 |

|     | 7.4.    | A/D Sampling Methods                                      | .28  |

|-----|---------|-----------------------------------------------------------|------|

|     |         | 7.4.1. FIFO Description                                   | . 28 |

|     |         | 7.4.2. Scan Sampling                                      | .29  |

|     |         | 7.4.3. Sequential Sampling                                | .29  |

|     |         | 7.4.4. Sampling Methods                                   | .29  |

| 8.  | D/A Ci  | rcuit                                                     | .31  |

|     | 8.1.    | Ranges and Resolutions                                    | .31  |

|     |         | 8.1.1. Ranges                                             | .31  |

|     |         | 8.1.2. Resolution                                         | .31  |

|     | 8.2.    | D/A Conversion Formulas and Tables                        | .32  |

|     |         | 8.2.1. D/A Conversion Formulas for Unipolar Output Ranges | .32  |

|     |         | 8.2.2. D/A Conversion Formulas for Bipolar Output Ranges  | .32  |

|     | 8.3.    | Calibration                                               | .33  |

|     | 8.4.    | Waveform Generator                                        | .34  |

| 9.  | Digital | I/O                                                       | .35  |

| 10. | Counte  | ers and Timers                                            | .36  |

| 11. | Pulse \ | Nidth Modulation                                          | .37  |

| 12. | Watch   | dog Timer                                                 | .38  |

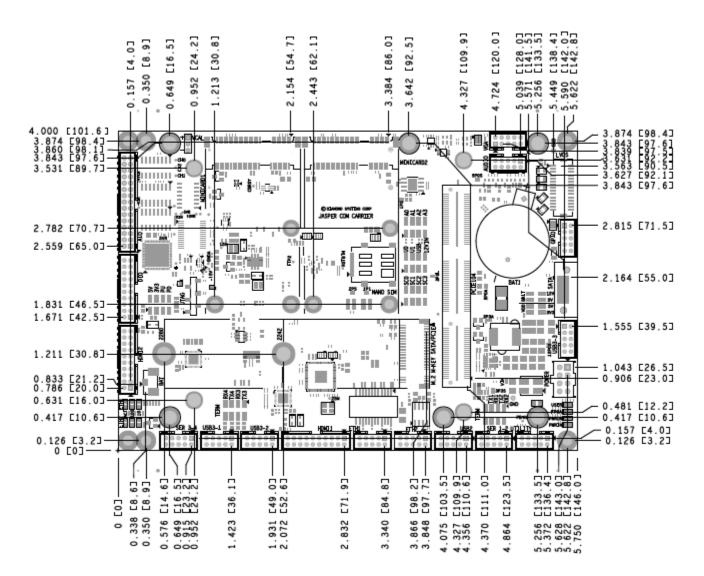

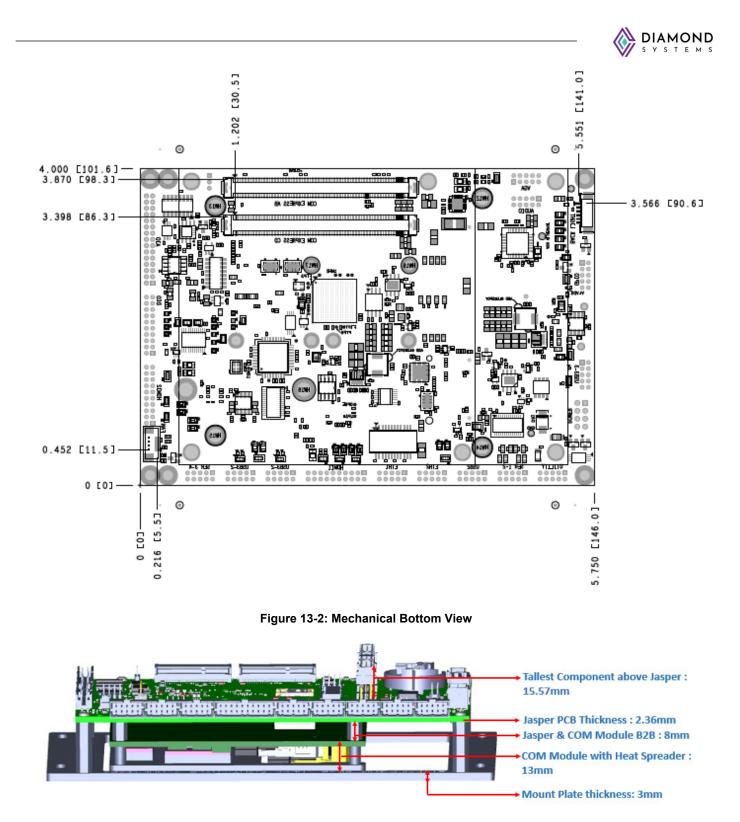

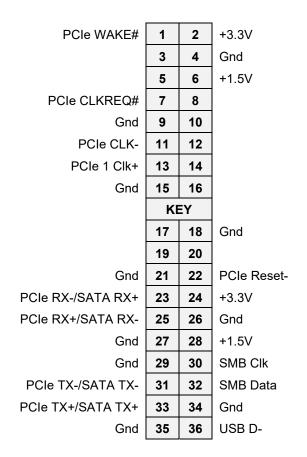

| 13. | Mecha   | nical Drawings                                            | .39  |

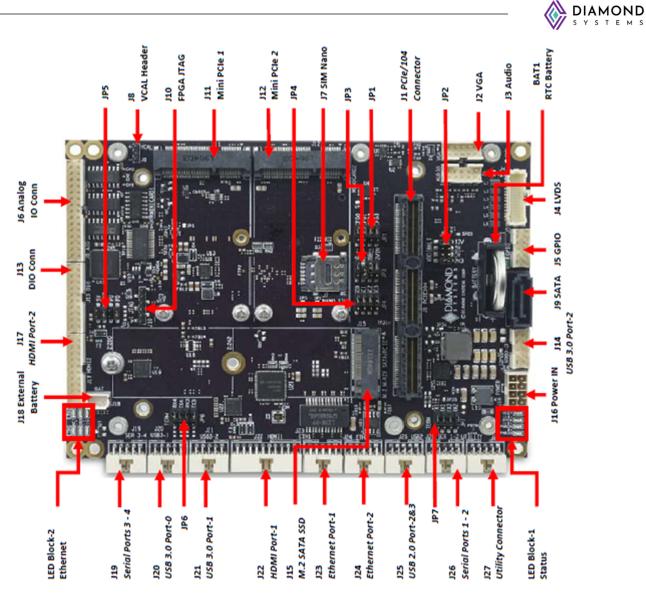

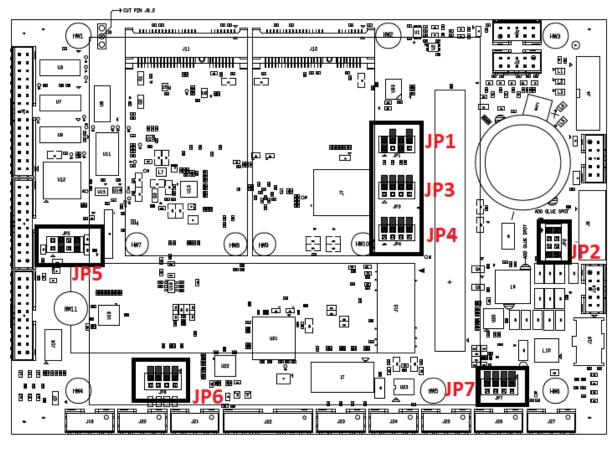

| 14. | Conne   | ctor and Jumper Locations                                 | .41  |

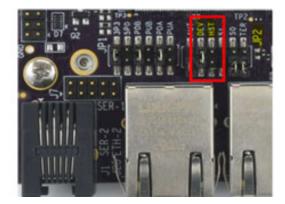

|     | 14.1.   | Jumper Selection                                          | .43  |

|     |         | 14.1.1. Jumper Block JP1                                  | .44  |

|     |         | 14.1.2. Jumper Block JP2                                  | .45  |

|     |         | 14.1.3. Jumper Block JP3                                  | .45  |

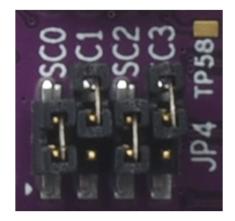

|     |         | 14.1.4. Jumper Block JP4                                  | .46  |

|     |         | 14.1.5. Jumper Block JP5                                  | .46  |

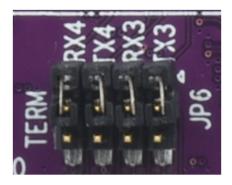

|     |         | 14.1.6. Jumper Block JP6                                  | .47  |

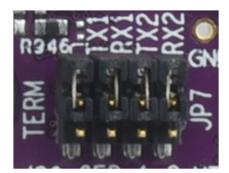

|     |         | 14.1.7. Jumper Block JP7                                  | .47  |

| 15. | Conne   | ctor Pinouts                                              | .49  |

|     | 15.1.   | Analog I/O (J6)                                           | .49  |

|     | 15.2.   | Audio (J3)                                                | .49  |

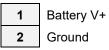

|     | 15.3.   | Battery (J18)                                             | .50  |

|     | 15.4.   | Digital I/O (J13)                                         | .50  |

|     | 15.5.   | Ethernet (J23 & J24)                                      | .50  |

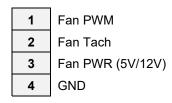

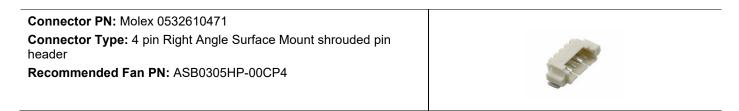

|     | 15.6.   | Fan Connector (J31)                                       | .51  |

|     | 15.7.   | GPIO Connector (J5)                                       | .51  |

|     | 15.8.   | HDMI (J17)                                                | .52  |

|     | 15.9.   | HDMI (J22)                                                |      |

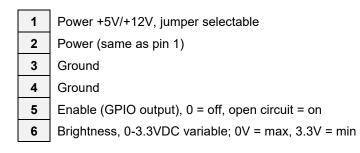

|     |         | LCD Backlight (J29)                                       |      |

|     |         | LVDS (J4)                                                 |      |

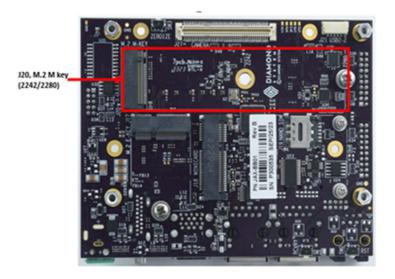

|     | 15.12   | M.2 Socket (J15)                                          | .54  |

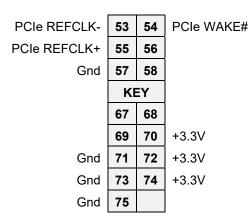

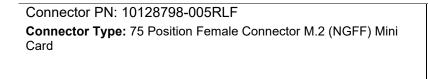

| 15.13.                                                                          | PCIe Mini Card (J11 & J12)55                                                                                   |                                           |  |  |  |  |

|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|--|--|--|

| 15.14.                                                                          | Power In (J16)                                                                                                 |                                           |  |  |  |  |

| 15.15.                                                                          | SATA (J9)                                                                                                      |                                           |  |  |  |  |

| 15.16.                                                                          | Serial ports (J26)                                                                                             | 57                                        |  |  |  |  |

| 15.17.                                                                          | Serial ports (J19)                                                                                             | 58                                        |  |  |  |  |

| 15.18.                                                                          | USB 2.0 Ports (J25)                                                                                            | 58                                        |  |  |  |  |

| 15.19.                                                                          | USB 3.0 Ports (J20, J21)                                                                                       | 59                                        |  |  |  |  |

| 15.20.                                                                          | USB 3.0 Ports (J14)                                                                                            | 59                                        |  |  |  |  |

| 15.21.                                                                          | Utility (J27)                                                                                                  | 59                                        |  |  |  |  |

| 15.22.                                                                          | VGA (J2)                                                                                                       | 60                                        |  |  |  |  |

|                                                                                 |                                                                                                                |                                           |  |  |  |  |

| 16. I/O Co                                                                      | nnector List & Mating Cables                                                                                   | 61                                        |  |  |  |  |

| -                                                                               | nnector List & Mating Cables<br>vs COM Module Interface Comparison List                                        |                                           |  |  |  |  |

| 17. Jasper                                                                      | -                                                                                                              | 63                                        |  |  |  |  |

| 17. Jasper<br>18. Mount                                                         | vs COM Module Interface Comparison List                                                                        | 63<br>65                                  |  |  |  |  |

| 17. Jasper<br>18. Mount                                                         | vs COM Module Interface Comparison List                                                                        | 63<br>65<br>66                            |  |  |  |  |

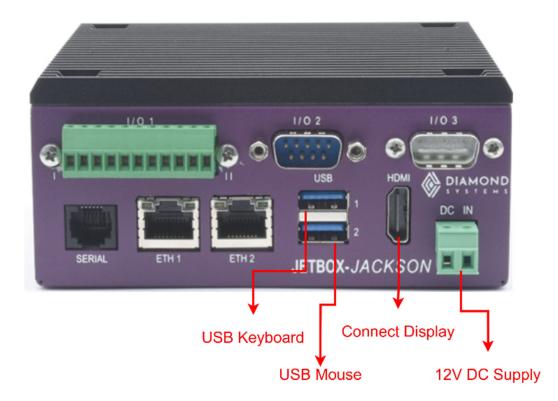

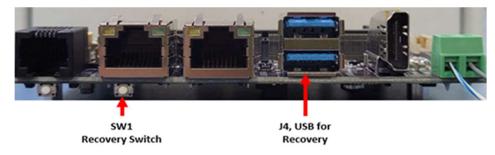

| <ol> <li>17. Jasper</li> <li>18. Mount</li> <li>19. Gettin</li> </ol>           | vs COM Module Interface Comparison List<br>ting Plate<br>g Started                                             | 63<br>65<br>66<br>66                      |  |  |  |  |

| <ol> <li>17. Jasper</li> <li>18. Mount</li> <li>19. Gettin<br/>19.1.</li> </ol> | vs COM Module Interface Comparison List<br>ting Plate<br>g Started<br>Powering Up System                       | <b>63</b><br><b>65</b><br><b>66</b><br>66 |  |  |  |  |

| <ol> <li>17. Jasper</li> <li>18. Mount</li> <li>19. Gettin<br/>19.1.</li> </ol> | vs COM Module Interface Comparison List<br>ting Plate<br>g Started<br>Powering Up System<br>Flashing BSP Image | 63<br>65<br>66<br>67<br>67                |  |  |  |  |

| <ol> <li>17. Jasper</li> <li>18. Mount</li> <li>19. Gettin<br/>19.1.</li> </ol> | vs COM Module Interface Comparison List                                                                        | 63<br>65<br>66<br>66<br>67<br>67          |  |  |  |  |

Notices

#### **Technical Support**

Please use the Technical Support Request form to request assistance with a product you have already purchased.

#### **Product and Sales Inquiry**

Please use the <u>Sales Inquiry</u> form to request assistance with selecting a product for your application, or to obtain further information about products and service.

#### **Limited Warranty**

Diamond Systems Corporation provides a Limited Warranty for all items in this guide that it manufactures and sells, pursuant to terms provided in the Diamond Systems Corporation Limited Warranty. No other warranty, express or implied, is included. Please download the warranty for additional information.

#### Trademarks

All trademarks, logos and brand names are the property of their respective owners.

# Important Safe Handling Information

#### WARNING!

ESD-Sensitive Electronic Equipment

Observe ESD-safe handling procedures when working with this product.

Always use this product in a properly grounded work area and wear appropriate ESD-preventive clothing and/or accessories.

Always store this product in ESD-protective packaging when not in use.

## **Safe Handling Precautions**

The Osbourne carrier board contains a high number of I/O connectors with connections to sensitive electronic components. This creates many opportunities for accidental damage during handling, installation, and connection to other equipment.

This section provides critical, best practice suggestions to avoid damage to your products. It includes descriptions of many common causes of damage – all of which can void your warranty.

Please follow these guidelines to be aware of common causes of damage and take the necessary precautions to prevent damage to your Diamond Systems' (or any vendor's) embedded computer boards.

#### Damage from incorrect handling or storage

- Physical and electronic damage can occur from mishandling. The following are frequent scenarios.

- An electrostatic discharge (ESD) causes a board to malfunction or stop working entirely. If ESD occurs, typically there is no visual sign of damage. While it is often difficult to identify faulty component(s), if the fault is identified there is a good chance that the board can be repaired.

- A screwdriver slips during installation, causing a gouge in the PCB surface and cutting signal traces or damaging components.

- A board is dropped, causing damage to the circuitry near the point of impact. Most of our boards are designed with at least 25 mils clearance between the board edge and any component pad, and ground / power planes are at least 20 mils from the edge. These design rules can minimize but cannot always prevent damage from impact.

- A short occurs when a metal screwdriver tip slips, or a screw drops onto a board while it is powered on. This can cause overvoltage or power supply problems described below.

- A storage rack with slots to hold boards can damage components near the board edge. Many boards have components that are close to the board edge, which are subject to damage in racks.

- Connector pins are bent by improperly dis-assembling attached boards or ribbon cables from a pin header, or from physical impact or improper storage. Typically, bent pins can be repaired one at a time with needle-nose pliers. Severely bent or frequently repaired pins may require the replacement of the connector.

#### Best Practices to avoid damage during handling or storage

- To prevent ESD damage, always follow proper ESD-prevention practices when handling any electronic components.

- To prevent physical damage from impact, handle all boards with care and work in a safe, spacious environment.

- To prevent short circuit damage from a metallic tool or dropped screw, perform assembly operations ONLY when the system is powered off.

- To prevent damage to fragile components and connector pins in storage, always store boards in individual ESD-safe sleeves in sturdy bins with dividers between boards. Do NOT use racks with slots, or stack boards in a pile or in close proximity.

- To prevent damage to connector pins during assembly or dis-assembly, use caution to align connectors and especially when force is needed to disassemble components and wires. Do not 'rock' connectors back and forth or pull any component at the wrong angle.

#### Damage due to incorrect voltage or connections

#### Power supply wired backwards

Diamond Systems power supplies and boards are not designed to withstand a reverse power supply connection. Reverse power will destroy nearly every IC that is connected to the power supply. Reverse power damage is rarely repairable. Check twice before applying power!

#### Board not installed properly in PC/104 stack

If a PC/104 board is accidentally shifted by 1 row or 1 column (of pins) it is possible for power and ground signals on the bus to contact the wrong pins. For example, this can damage components attached to the data bus because it puts the  $\pm 12V$  power supply lines directly on data bus lines.

#### Overvoltage on analog input

If a voltage applied to an analog input exceeds the design specification of the board, the input multiplexor and/or parts behind it can be damaged. Most of our boards will withstand an erroneous connection of up to  $\pm 35V$  on the analog inputs, even when the board is powered off, but not all boards, and not in all conditions.

#### Overvoltage on analog output

If an analog output is accidentally connected to another output signal or a power supply voltage, the output can be damaged. On most of our boards, a short circuit to ground on an analog output will not cause trouble.

#### Overvoltage on digital I/O line

If a digital I/O signal is connected to a voltage above the maximum specified voltage, the digital circuitry can be damaged. On most of our boards the acceptable range of voltages connected to digital I/O signals is 0-5V, and they can withstand about 0.5V beyond that (-0.5 to 5.5V) before being damaged. However, logic signals at 12V and even 24V are common, and if one of these is connected to a 5V logic chip, the chip will be damaged, and damage may extend past that chip to others in the circuit.

#### Best Practices to avoid damage due to incorrect voltage or connections

- Ensure all power supply connections are correct and not reversed!

- Ensure all pins are aligned properly before and after assembling boards and components!

- Ensure proper voltage is supplied to all analog inputs!

- Ensure all analog voltage outputs do not connect to another signal output or power supply output!

- Ensure all voltages for digital I/O lines are proper and with range, and that higher voltage signals (24V or 12V) are not supplied to lower voltage circuits (12V or 5V)!

IMPORTANT! Always check twice before Powering Up!

# 1. Introduction

## 1.1. Jasper Product Overview

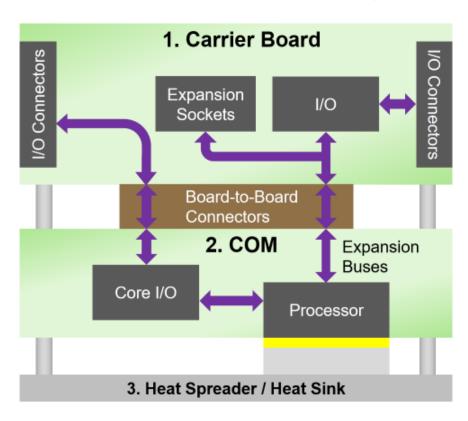

Jasper is a compact rugged single-board computer (SBC) utilizing a COM Express module to provide performance scalability, extended product lifetime, and a reduced footprint due to a stacked board configuration. The SBC is available with a choice of COMs that have been tested for compatibility, offering a range of Core i7 and Xeon processors from both 11th and 13th generation families.

The use of a COM-based architecture yields many significant benefits over a true single-board computer where the processor and related circuitry are included on the main board:

- Scalable CPU performance you can swap out one COM for another in the exact same form factor but with a different CPU. This allows your system to be easily upgraded when software demands increase, while avoiding any mechanical redesign.

- **Extended product lifetime** if the COM you're using becomes obsolete, another one can be used in its place easily, with no mechanical changes required to the system. This enables COM-based embedded systems to easily last 20 years, since most of the baseboard electronics usually have much longer lifecycles than the processor and related peripherals contained on the COM.

- **Higher feature density / smaller overall size -** the stacked 2-board design means you get more features per unit area in your system.

- Earlier access to the latest CPU technology Most new processors are introduced in COMs long before they are available in true single-board computer form. With a COM-based SBC you can upgrade your system with the latest CPU sooner, again without having to engage in any mechanical redesign.

- **Consistent platform across product lines** the CPU scalability and interchangeability mean that a single physical form factor can be used in multiple applications requiring different CPU capability.

Jasper is available with an integrated professional-quality data acquisition circuit featuring analog and digital I/O with full programming library support. It includes a wide range of built-in standard PC I/O plus expansion sockets for minicards and PCIe/104 I/O modules, making it a great choice for applications requiring any combination of high performance,

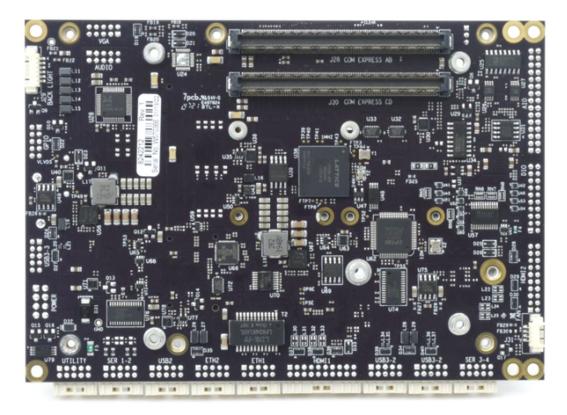

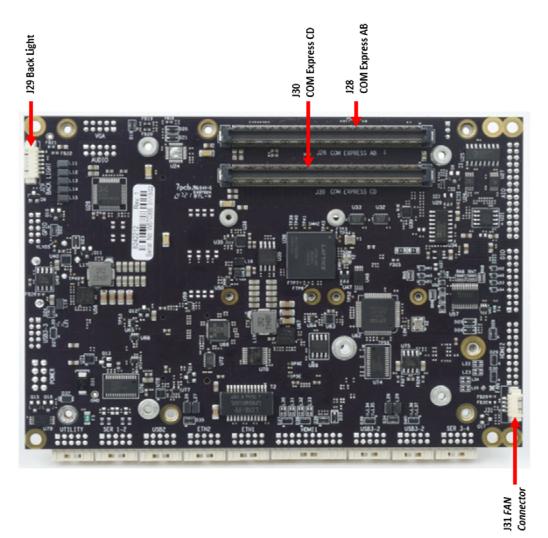

The COM Express module mounts on the bottom side of the board, and the PCIe104 expansion sockets are on the top side. The board dimensions are 4.000" x 5.750", matching the 3.5-inch form factor in size and mounting hole pattern.

A thicker PCB (.090" / 2.3mm), latching I/O connectors, and full -40/+85C operating temperature provide increased ruggedness, enabling the board to work reliably in mobile and harsh environment applications. Jasper is used as the processor in Diamond's rugged SabreCom and Geode rugged computer systems. The Jasper SBC has passed MIL-STD-202H shock and vibration testing, and the Geode system with Jasper SBC inside has passed MIL-STD-810H testing. Test reports are available on the product's web page.

\* Jasper supports both Basic 95x125mm and Compact 95x95mm COM Express modules.

## 1.2. Processor Options

Jasper is available with a variety of installed COM Express modules. These COMs are all tested and approved by Diamond and have board support packages (configured operating system images) available for Windows 10 / 11 and Linux. The list of available processors may change from time to time as new COMs are tested and qualified. The table below lists the available options as of the publication date of this manual.

In many cases a COM not listed here may also work properly with minimal or no BIOS customization. However, COM vendors may implement various features in different configurations or quantities (especially the number and type of PCIe lanes), so certain features may not function if the COM doesn't provide the necessary interface for them. Please check with Diamond technical support if you are interested in using Jasper with a COM not listed here.

| Generation        | Туре    | Processor | PassMark*<br>(approx.) | Max RAM             |

|-------------------|---------|-----------|------------------------|---------------------|

| 11<br>Tiger Lake  | Core i7 | 1185GRE   | 8,000                  | 32GB                |

| 11<br>Tiger Lake  | Core i7 | 1185G7E   | 10,300                 | 64GB                |

| 13<br>Raptor Lake | Core i7 | 1365URE   | 10,300                 | 64GB                |

| 11<br>Tiger Lake  | Xeon    | 11865MRE  | 19,600                 | 96GB or<br>ECC 32GB |

(PassMark ratings are as reported by PassMark.com and are provided for comparison purposes only.)

## 1.3. Baseboard Variants

The baseboard used in Jasper is available in multiple configurations. Models BB02D and BB03A are normally in stock, while the lower cost BB01D normally requires a minimum order quantity.

| Feature           | Baseline<br>JSP-BB01D                       | Full-Feature<br>JSP-BB02D                               | Full Feature w/ DAQ<br>JSP-BB03A                        |

|-------------------|---------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

| Availability      | Special order                               | Stocked                                                 | Stocked                                                 |

| Gigabit Ethernet  | 1                                           | 2                                                       | 2                                                       |

| Minicard socket   | 2                                           | 2                                                       | 2                                                       |

| M.2 socket        | 1                                           | 1                                                       | 1                                                       |

| SATA connector    | 1                                           | 1                                                       | 1                                                       |

| HDMI              | 2                                           | 2                                                       | 2                                                       |

| VGA*              | 1                                           | 1                                                       | 1                                                       |

| LVDS              | 1                                           | 1                                                       | 1                                                       |

| USB 3.0           | 3                                           | 3                                                       | 3                                                       |

| USB 2.0           | 2                                           | 2                                                       | 2                                                       |

| Serial Ports      | 2x RS-232                                   | 4x RS-232/422/485<br>(Jumper for protocol<br>selection) | 4x RS-232/422/485<br>(Jumper for protocol<br>selection) |

| PCIe104 socket    | No                                          | Yes                                                     | Yes                                                     |

| Audio             | No                                          | 1                                                       | 1                                                       |

| Analog/Digital IO | No                                          | No                                                      | 16 SI/8 DE Ain<br>4 Aout<br>22 DIO                      |

| Others            | 4 GPI, 4 GPO<br>I2C<br>Reset & Power Button | 4 GPI, 4 GPO<br>I2C,1x RS232<br>Reset & Power Button    | 4 GPI, 4 GPO<br>I2C, 1x RS232<br>Reset & Power Button   |

\*Based on availability on the installed COM Express module

## 1.4. Jasper Ordering Guide

The table below lists the available standard configurations for the carrier board. This list is valid as of the publication date of this manual. As the board can work with multiple COMs, new COMs are tested and added regularly, so check the Diamond website or contact our sales department for currently available product models.

In general, when a new COM is added, OS support will also be available for the current versions of Windows and Ubuntu Linux.

#### **Carrier board**

| JSP-BB01D | Jasper COM Carrier, low-cost model, 12V or 15-36VDC In (special order item) |

|-----------|-----------------------------------------------------------------------------|

| JSP-BB02D | Jasper COM Carrier, PCIe/104 expansion, Digital I/O, 12V or 15-36VDC In     |

| JSP-BB03A | Jasper COM Carrier, PCIe/104 and Data Acquisition, 12V or 15-36VDC In       |

#### Jasper SBC product (carrier board with installed COM and heat spreader; no OS installed)

| JSP-1185G7E-64G-02D | JSP-BB02D with Intel 11th Gen Core i7, 64GB RAM, Heat Spreader                  |

|---------------------|---------------------------------------------------------------------------------|

| JSP-1185G7E-64G-03A | JSP-BB03A with Intel 11th Gen Core i7, 64GB RAM, Heat Spreader                  |

| JSP-1185GRE-32G-02D | JSP-BB02D with Intel 11th Gen Core i7-1185GRE, 32GB RAM Soldered, Heat Spreader |

| JSP-1365URE-64G-02D | JSP-BB02D with Intel 13th Gen Core i7-1365URE, 64GB RAM Soldered, Heat Spreader |

#### Software development kits (Pre-configured OS on a flashdisk with backup USB memory stick)

| SDK-JSP-1185G7E-<br>LNX64  | Linux 64-bit Software Development Kit for Jasper SBC with 11th Gen Core i7<br>(Inclusive of OS, Instruction for flashing, USB2.0 8GB Flash drive, M.2 2242<br>SATA 64GB wide temperature flash disk)  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDK-JSP-1185G7E-<br>WE1064 | Windows 10 64-bit Software Development Kit for Jasper SBC with 11th Gen<br>Core i7                                                                                                                    |

|                            | (Inclusive of OS, Instruction for flashing, USB2.0 8GB Flash drive, M.2 2242 SATA 64GB wide temperature flash disk)                                                                                   |

| SDK-JSP-1185GRE-<br>LNX64  | Linux 64-bit Software Development Kit for Jasper SBC with 1185GRE<br>processor (Inclusive of OS, Instruction for flashing, USB2.0 8GB Flash drive,<br>M.2 2242 SATA 64GB wide temperature flash disk) |

| SDK-JSP-1185GRE-<br>WE1064 | Windows 10 64-bit Software Development Kit for Jasper SBC with 1185GRE processor (Inclusive of OS, Instruction for flashing, USB2.0 8GB Flash drive, M.2 2242 SATA 64GB wide temperature flash disk)  |

#### Development kits (SBC + software development kit + cable kit)

| DK-JSP-1185G7E-LNX64      | Development Kit: Jasper 11th Gen Core i7 SBC with DIO, 64GB RAM, Linux 64-bit OS |

|---------------------------|----------------------------------------------------------------------------------|

| DK-JSP-1185G7E-<br>WE1064 | Development Kit, Jasper SBC, 1185G7E CPU, Windows 10 64-Bit OS                   |

#### Cable kit

| CK-JSP-01 | Jasper cable kit, full kit with data acquisition cables (for "A" models) |

|-----------|--------------------------------------------------------------------------|

| CK-JSP-02 | Jasper cable kit, without data acquisition cables (for "D" models)       |

## 1.5. Product Photos

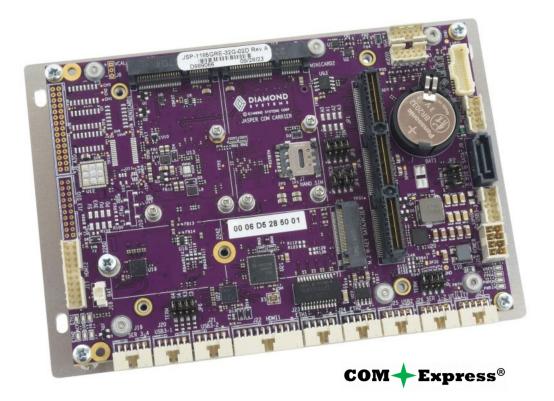

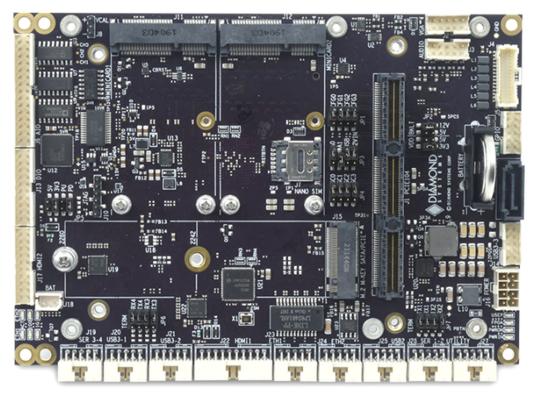

Figure 1-1: COM module installation side

Figure 1-2: I/O expansion side ("A" model with data acquisition shown)

# 2. Feature List

| Feature           | Description                                                                                    | Connector Type                                      |

|-------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| Power             | 15V-36V wide input or 12V fixed supply<br>(Selected using Jumper configuration at<br>JP3)      | 8 Position Vertical Connector Header (J16)          |

| RTC               | 3V power input for RTC functionality                                                           | On board battery 2032 holder                        |

|                   |                                                                                                | Or 2 Position Vertical Connector Header (J18)       |

| Ethernet          | ETH-1 10/100/1000Mbps from COM module                                                          | 10 Position RA Connector Header (J23)               |

|                   | ETH-2 10/100/1000Mbps via I210 Ethernet controller                                             | 10 Position RA Connector Header (J24)               |

| Mass Storage      | 2 PCIe minicard socket with USB and SATA<br>Minicard2 supports Nano SIM interface              | 2 PCIe MiniCard 52 Position (J11 & J12)             |

|                   | 1 M.2 2242 / 2280 SATA/x1 PCIe                                                                 | M.2 Socket (J15)                                    |

|                   | 1 Standard 7pin SATA connector                                                                 | SATA Connector (J9)                                 |

| Audio             | HDA to Analog Audio converter                                                                  | 10 Position Vertical Connector Header (J3)          |

| USB               | 2x USB 2.0                                                                                     | 10 Position RA Connector Header (J25)               |

|                   | 3x USB3.0 / USB2.0                                                                             | 10 Position Connector Header (J20, J21, J14)        |

| Serial Ports      | 4 ports Software configurable RS-<br>232/422/485 through SP336 transceivers or<br>2 RS232 only | 10 Position RA Connector Header (J19, J26)          |

| Display           | 2x HDMI                                                                                        | 20 Position Connector Header (J17, J22)             |

|                   | 1x VGA (Based on the COMe module)                                                              | 10 Position RA Connector Header (J2)                |

|                   | 1x Dual Channel 24-bit LVDS port with 3.3V<br>/ 5V power option                                | 30 Position RA Connector Header (J4)                |

| LCD Backlight     | LCD backlight power and control signals with 5V / 12V power option                             | Surface Mount 6 Position Connector Receptacle (J29) |

| Analog/Digital IO | Supported only on                                                                              | 30 Position Vertical Connector Header (J6)          |

|                   | 16 Single ended/ 8 Differential ended Ain<br>4 Aout                                            | 20 Position Vertical Connector Header (J13)         |

|                   | 22 Programmable direction digital I/O,<br>3.3V/5V logic compatible                             |                                                     |

| PCIe104           | 4 PCIe x1 ports, 1x PCIe x16                                                                   | 156 Position Vertical Header (J1)                   |

| GPIO              | 4 GPI, 4 GPO                                                                                   | 10 Position Right Angle Connector Header (J5)       |

| Others (Utility)  | I2C, Reset Button, Power Button                                                                | 10 Position Vertical Connector Header (J27)         |

|                   |                                                                                                |                                                     |

| Operating System Support                                                                                     |                                                                                                                       |  |  |

|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| Windows 10; Ubuntu; Linux                                                                                    |                                                                                                                       |  |  |

| Form-Factor                                                                                                  | 4.000" x 5.750"                                                                                                       |  |  |

| Cooling Mechanism                                                                                            | Conduction cooling with bottom side heat spreader (target heat spreader height 13mm as per COM express specification) |  |  |

| Power Input Range                                                                                            | 15V-36V wide range input or Fixed 12V +/-10% supply                                                                   |  |  |

| Operating Temperature -40°C to +85°C ambient (final system capability depends on the COM installed)<br>Range |                                                                                                                       |  |  |

| Physical                    |                                                                                                                       |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Form-Factor                 | 4.000" x 5.750"                                                                                                       |

| Cooling Mechanism           | Conduction cooling with bottom side heat spreader (target heat spreader height 13mm as per COM express specification) |

| Power Input Range           | 15V-36V wide range input or Fixed 12V +/-10% supply                                                                   |

| Operating Temperature Range | -40°C to +85°C ambient (final system capability depends on the COM installed)                                         |

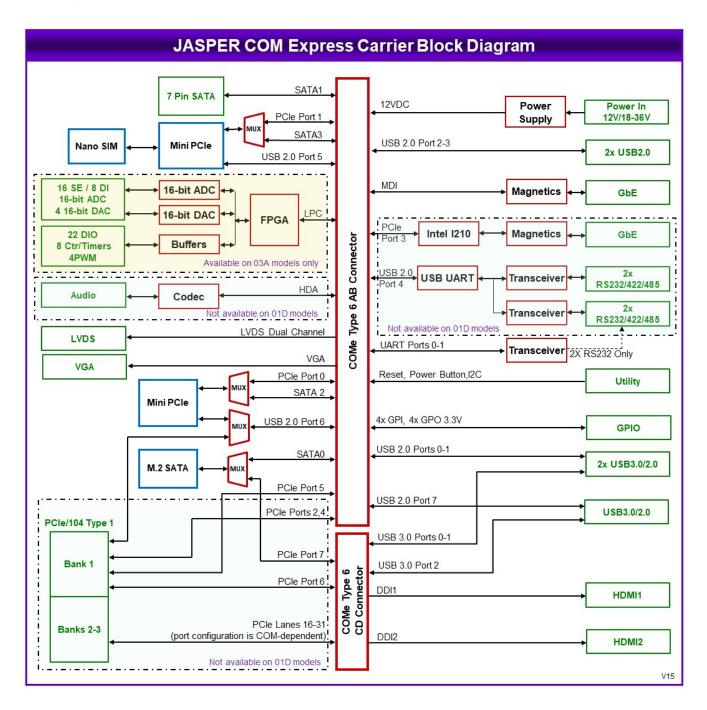

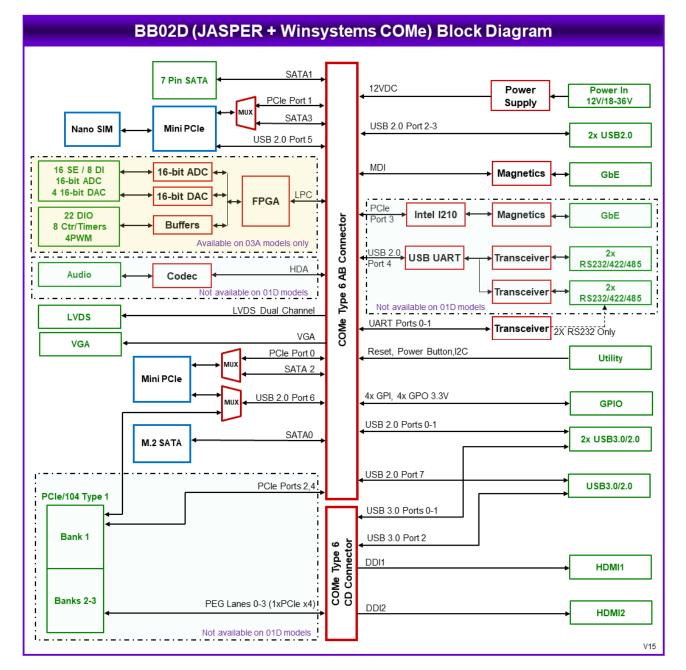

# 3. Block Diagrams

The following Block Diagrams illustrate the key functional block of the JASPER COM Express Carrier board. A full-featured configuration is shown for COMs with 8 PCIe x1 links available. A reduced configuration is shown for COMs having only 5 PCIe x1 links.

JASPER COM Express Carrier Board Block Diagram, all features shown (COM with 8 PCIe lanes available)

JASPER COM Express Carrier Board Block Diagram, COM with 5 PCIe lanes configuration (lanes 5-7 not available)

## 4. Product Photos

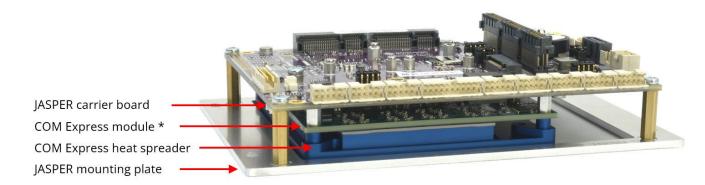

Top view of Jasper "D" model

Bottom view showing Compact size COM + heat spreader nested in mounting plate

Bottom view showing Basic size COM + heat spreader nested in mounting plate

# 5. Functional Overview

The following section provides functional details of the key subsystems implemented on Jasper.

## 5.1. COM Express Carrier Board

Jasper supports COM Express Type 6 Compact (95x95mm) and Basic (95x125mm) modules. The availability of I/O features is dependent on the installed COM. In most cases the only impact on features is the number of PCIe x1 lanes. See PCIe lane mapping information below.

## 5.2. Power Supply Specifications

The board is powered from a wide input voltage range of 15V-36V wide range input or fixed 12V +/-5% supply. This is done using jumper setting available on JP3.

All required power supply voltages for Jasper are derived from the 18V-36V wide range input or fixed 12V +/-5% DC input. These power supplies are sized to meet or exceed the ratings below to support add-on features.

| 12V | 5V  | 3.3V | Feature              |

|-----|-----|------|----------------------|

| 3.6 | 0.5 | -    | COM Express Module   |

|     |     | 1.5  | M.2                  |

|     | 1   |      | USB2.0Ports          |

|     |     | 2.6  | PCIe minicard socket |

|     | 2.7 |      | USB 3.0 Ports        |

| 1   | 2   | 1.5  | PCIe104              |

|     | 0.1 | 0.1  | Utility Connector    |

| 1.1 | 1   | 1    | LVDS/LCD             |

|     |     |      |                      |

## 5.3. Ethernet Ports

Jasper supports two 10/100/1000 Ethernet ports. One port comes directly from the COM module. The other port is derived from the Intel WGI210IT PCIe Ethernet controller. This controller is connected through x1 PCIe lane from the COM module. Each port has on-board magnetics. Both Ethernet ports are terminated at two DSC standard 2x5 pin headers.

On-board LEDs are provided for Link, Activity, and Speed on each port. The LEDs are located along the left bottom edge of the board.

## 5.4. PCIe Link Routing

Jasper's PCIe x1 port mapping is provided below. The number of lanes available depends on the COM module installed. Refer to the block diagrams and the selected COM for more details. The installed PCIe lane assignment on Jasper was designed to minimize the loss of features on COM that have fewer than 8 PCIe x1 lanes.

The carrier board routes the PCIe x16 lanes from the COM Express CD connector to the PCIe104 connector banks 2 and 3. The usability of these lanes depends on the COM design. Please check with Diamond tech support for lane configuration and availability of the selected model.

The PCIe x1 lane assignments are shown below.

- Lane 0 Minicard Socket 1

- Lane 1 Minicard Socket 2

- Lane 2 PCIe104 OneBank lane 0

- Lane 3 Intel I210 Ethernet Controller (2<sup>nd</sup> Ethernet port; 1<sup>st</sup> port comes from the COM)

- Lane 4 PCIe104 OneBank lane 1

- Lane 5 PCIe104 OneBank lane 2

- Lane 6 PCIe104 OneBank lane 3

- Lane 7 M.2 2280/2242 (if lane 7 is not available, the M.2 will support SATA only)

- PEG x16 PCIe104 Type1 (availability of PCIe x4 / x8 / x16 depends on COM PEG lane routing)

## 5.5. SATA M.2 Socket

Jasper offers up to four SATA ports, derived from the COM Express module.

- M.2 2242/2280 socket supports SATA Port 0 / PCIe Lane 7 using a high-speed mux. SBC provides onboard M3 4mm spacer to mount M.2 2280 SATA SSD and M3 2mm spacer acts as nut for the Male to Female 4mm spacer provided to mount M.2 2242 SATA SSD.

- Second SATA port (mapped as Port 1 from COM) is connected to an industry-standard vertical 7pin SATA connector that accepts cables with latching.

- Third SATA (mapped as Port 2 from COM) and fourth (mapped as Port 3 from COM) SATA ports are

made available on the first and second minicard sockets respectively using high speed mux. PCIe/SATA

interface is supported depending on the type of minicard module inserted.

- PCIe support on the M.2 is dependent on the COM module installed. Refer feature list for individual configurations for more details.

## 5.6. USB

Jasper supports 2 USB2.0 ports and 3 USB 3.0/USB 2.0 ports from the COM. 2x USB2.0 ports are routed to one 2x5 headers and 3x USB 3.0/USB2.0 ports are routed to three 2x5 headers.

USB2.0 port 6 is muxed between minicard socket 1 and PCIe104 and can be selected using jumper configuration at JP3.

USB port mapping is shown below:

| Port Termination |

|------------------|

| USB3.0 Header 1  |

| USB3.0 Header 2  |

| USB3.0 Header 3  |

| Not Used         |

|                  |

|                  |

| Port Termination |

| USB3.0 Header 1  |

| USB3.0 Header 2  |

| USB2.0 Header    |

| USD2.0 Headel    |

| USB to Quad UART |

|                  |

| Minicard Socket2 |

|                  |

Port 7 USB3.0 Header 3

## 5.7. Audio

The HD audio from the COM module is converted to analog audio using an Audio Codec. Line IN, Line OUT and Mic signals are terminated on a 2x5 pin header.

## 5.8. LVDS LCD

Jasper supports a 24-bit dual channel LVDS display with a 2x15 vertical latching connector. A separate backlight supply connector provides LCD backlight supply and PWM control. A backlight supply will be derived from the main power input.

## 5.9. HDMI

Jasper offers two HDMI 2.0 video outputs. HDMI ports are made available on two 2x10 2mm pitch pin headers. SN65DP159RSBT IC is used for DP++ to HDMI level translation.

## 5.10. Serial Ports

Jasper supports 4 serial ports using a USB to quad UART controller (FT4232HL) in full feature variant (JSP BB02D and JSP BB03A) and 2 RS232 ports on low-cost baseboard variants (JSP BB01D). The four serial ports are available on two 2x5 pin headers. The ports use SP336 transceivers (1 transceiver for 2 ports) to support RS-232, RS-422, and RS-485 protocols. The protocol is selected using GPIO pins on the FPGA in full feature (JSP BB03A) and Jumper options are given for protocol selection in full feature without DAQ (JSP BB02D). Onboard jumpers are provided to enable 121-ohm line termination for RS-422 and RS-485 protocols.

In the low-cost version (JSP BB01D) two RS232 (only) ports are made available at one of the 2x5 pin headers.

## 5.11. Data Acquisition

Jasper provides an optional data acquisition subcircuit containing analog input, analog output, and digital I/O features. This circuit is controlled by an FPGA attached to the processor via the LPC bus. A pin header on the board provides access to JTAG signals for reprogramming the FPGA that managed the data acquisition circuit. This pin header is for factory use only and should not be accessed by the user.

The DAQ feature support is dependent on the base board model. Refer to the Ordering guide section for more details.

## 5.12. Backup Battery

An onboard 2032 coin cell battery holder is provided to maintain the system real-time clock. A 1x2 connector is provided to enable the use of an external battery for rugged applications.

This is used on a battery backed internal RTC circuit in COM Module that keeps system time and date as well as certain system setup parameters. The board can boot and function properly without a backup battery installed.

## 5.13. Trusted Platform Module

The board contains circuitry to support TPM 1.2/2.0 standard compliant functionality. Most COMs used on Jasper have TPM already included, so the carrier board TPM circuit is not installed by default. It can be added as a backup solution in cases where the installed COM does not have integrated TPM.

## 5.14. Utility

The board offers a 2x5 utility connector, Power Button, Reset button and I2C interface.

It provides 500mA fused 3.3V supply.

Power Button is an active low input signal (momentary pulse triggering less than a second) used to wake up the system from a sleep state or soft shutdown.

Also, in generic, long press of power button more than 4 seconds will override system to soft shutdown (S5 state). This time interval depends on the COM Module's design aspects.

I/O level of this signal is defined to be 3.3V as per the COM specification.

System Reset is an active low request for Module to reset and reboot. The logic level of this signal is 3.3V as per the COM specification.

## 5.15. GPIO Header

The board contains a GPIO header with 4 GPI and 4 GPO available from the COMe module. GPI3 (by default) is muxed with TPM IRQ.

General purpose input and outputs pins are defined to be in push-pull CMOS configuration with 3.3V levels as in COM specification.

These are directed to / from COM module to the J5 GPIO connector on Jasper with no pullup or pull-down resistors mounted on carrier board.

It provides 500mA fused 3.3V supply.

#### 5.16. Minicard Socket

Jasper offers two full size (51mm length) or two half size Minicard sockets. Minicard interface supports PCIex1 and SATA using a mux. Both minicard support USB2.0 interface.

On minicard connector 1, PCIe lane 0 and SATA Port 2 are muxed using a high-speed mux IC. USB2.0 Port 6 is muxed with minicard connector 1 and PCIe104 and can be selected using jumper configuration available at JP3.

On Minicard connector 2, PCIe lane 1 and SATA port 3 are muxed using a high-speed mux IC. USB2.0 port 5 is also made available with the connector. A Nano SIM connector is supported on the minicard connector 2.

Jasper provides two onboard M2 4mm spacers on each minicard sockets to mount modules and for half minicard there are M2 2mm spacer which acts as nut for the Male to Female M2 4mm spacer provided as accessory.

#### 5.17. PCIe104 Expansion

The board offers I/O expansion with a full-size 3-bank PCIe104 connector with 22mm stacking height. This taller height is intended to allow for installed minicards and cabling below the PCIe/104 board.

The PCIe/104 connector supports up to four PCIe x1 ports on the first bank of the PCIe104 connector (referred to as the OneBank connector) and x16 PEG port on the 2<sup>nd</sup> and 3<sup>rd</sup> bank. The PCIe ports availability depends on the COM express module installed.

One of the USB2.0 (Port 6) is muxed with minicard 2 can be selected using jumper configuration at JP3.

Availability of PCIe104 expansion feature is dependent on the baseboard variant. Refer Jasper ordering guide section for more details.

#### 5.18. LED Indicators

Jasper provides the following LED indicators. All LEDs are located near a board edge or their respective features. All LEDs are labeled in silkscreen with their function.

| Function    | LED color and operation | PCB label |

|-------------|-------------------------|-----------|

| Power input | Input power applied     | PWR IN    |

| Function   | LED color and operation                               | PCB label        |

|------------|-------------------------------------------------------|------------------|

| Power Good | Green LED for Power Good indication                   | PWR ON           |

| Done LED   | FPGA is configured successfully                       | DONE             |

| User LED   | Blue, controlled by processor FPGA                    | USER             |

| Ethernet:  | Green LED for Link, activity, and speed for each port | LINK, ACT, SPEED |

JSP BB01D: This variant has LED indications on Power input (PWR IN), Power good (PWR ON) and ethernet (LINK, ACT, SPEED).

JSP BB02D: This variant has LED indications on Power input (PWR IN), Power good (PWR ON) and ethernet (LINK, ACT, SPEED).

JSP BB03A: This variant has LED indications on Power input (PWR IN), Power good (PWR ON), Done LED (DONE), User LED (USER) and ethernet (LINK, ACT, SPEED).

| l                           | ED Block-1 |

|-----------------------------|------------|

| 1st LED (Left most)         | PWRIN      |

| 2nd LED (Left middle most)  | PWRON      |

| 3rd LED (Right middle most) | FPGA       |

| 4th LED (Right most)        | USER       |

| l                           | ED Block-2 |

| 1st Row 1st LED             | ETH1 ACT   |

| 1st Row 2nd LED             | ETH2 ACT   |

| 2nd Row 1st LED             | ETH1 100   |

| 2nd Row 2nd LED             | ETH2 100   |

| 3rd Row 1st LED             | ETH1 1G    |

| 3rd Row 2nd LED             | ETH2 1G    |

Figure 5-1: LED Blocks

# 6. Data Acquisition Circuit

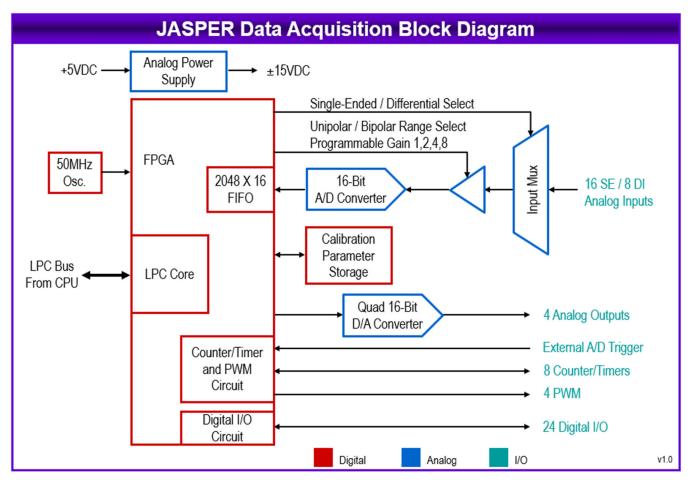

## 6.1. Overview

Jasper contains a data acquisition subsystem consisting of A/D, D/A, digital I/O, and counter/timer features.

The A/D section includes a 16-bit A/D converter, 16 analog input channels and a 2048-sample FIFO. Input ranges are programmable, and the maximum sampling rate is 250 KHz. The D/A section include 4 16-bit D/A channels. The digital I/O section includes up to 22 lines with programmable direction. The counter/timer section includes 32-bit counter/timer to control A/D and a 32-bit counter/timer for user applications.

High-speed A/D sampling is supported with interrupts and a FIFO. The FIFO is used to store up to 2048 A/D samples. An interrupt occurs when the FIFO reaches a user-selected threshold. Once the interrupt occurs, an interrupt routine runs and reads the data out of the FIFO. In this way the interrupt rate is reduced by a factor equal to the size of the FIFO threshold, enabling a faster A/D sampling rate and lower software overhead.

The A/D circuit uses the default settings of I/O address range 0x240 – 0x280 (base address 0x240). These settings can be changed if needed. The I/O address range is changed in the BIOS.

The figure below shows the overview of the data acquisition circuit.

Figure 6-1: Data Acquisition Circuit Block Diagram

## 6.2. FPGA

The FPGA provides all of the logic functions of the Jasper SBC data acquisition as well as a watchdog timer and a power sequencing circuit. The chip also interfaces to a Renesas encryption chip for future security features.

The following table shows a list of all the features offered by Jasper FPGA.

| Feature        | Description                            |

|----------------|----------------------------------------|

| A/D channels   | 16 16-bit Analog inputs                |

| D/A channels   | 4 16-bit analog outputs                |

| DIO Lines      | 22 lines: 1 8-bit port, 14 1-bit ports |

| Counter/Timers | 8 32-bit                               |

| PWM            | 4 24-bit                               |

|                | 2 Down counters                        |

| Watchdog timer | Counter A - 16-bits                    |

|                | Counter B - 8-bits                     |

## 6.3. Bus Interface

Jasper uses LPC for bus interface. LPC lines LAD[3:0] communicate address, control, and data information over the LPC between a host a peripheral. The information communicated is start, stop (abort a cycle), transfer type (memory I/O), transfer direction (Read/Write), address, data, wait states and bus master grant. Not all cycle types use the LAD bus in the same fashion.

The following are the different LPC pins used in the FPGA for communicating between a host and the peripheral.

- LPC\_FRAME# Indicates start of a new cycle, termination of broken cycle.

- LPC\_RESET# Same as PCI Reset on the host.

- LPC\_CLK Buffered 33MHz clock from the host. Input to the FPGA.

- LPC\_SERIRQ Serialized IRQ signal

#### 6.4. Interrupts

The FPGA supports LPC interrupts from the analog input circuit, D/A fault indicator, digital I/O, and two counter/timers. Register bits ADINTEN, FINTEN, DINTEN, T2INTEN, and T3INTEN enable/disable interrupts. When an INTEN bit is 1, interrupts for that circuit are enabled. However, 0 disables the interrupt feature. The LPC bus interrupt level is selected with register bits IRQ3-0.

When a circuit is requesting interrupt service, its corresponding status bit DINT, ADINT, T2INT, or T3INT is high. Command bits DINTCLR, ADINTCLR, T2INTCLR, and T3INTCLR reset the associated interrupt request and status bit. In contrast to other command registers in this design, any or all of these command bits may be set simultaneously to clear multiple interrupt requests simultaneously.

| FIFOEN | SCANEN | Action                                                                                             |

|--------|--------|----------------------------------------------------------------------------------------------------|

| 0      | 0      | Interrupt occurs after each A/D conversion completes (ADBUSY goes low).                            |

| 0      | 1      | Interrupt occurs after each A/D scan completes (ADBUSY goes low).                                  |

| 1      | 0      | Interrupt occurs when A/D conversion completes, and FIFO threshold is reached <b>or exceeded</b> . |

| 1      | 1      | Interrupt occurs when A/D scan completes, <b>and</b> FIFO threshold is reached or exceeded.        |

ADINT=1 and an interrupt occurs when ADINTEN=1 and one of the following occurs:

T2INT=1 and an interrupt occurs when T2INTEN=1 and counter/timer 2 counts down to 0. There is no terminal count and therefore no interrupt source when counter/timer 2 is counting up.

T3INT=1 and an interrupt occurs when T3INTEN=1 and counter/timer 3 counts down to 0. There is no terminal count and therefore no interrupt source when counter/timer 3 is counting up.

DINTSEL4-0 selects the digital I/O line to be used for edge-triggered interrupts. The selection is as follows:

| 0-7   | Port A 0-7 |

|-------|------------|

| 8-15  | Port B 0-7 |

| 16-21 | Port C 0-5 |

When DINTEN = 1 and the digital I/O line specified by DINTSEL4-0 exhibits the edge specified by DINTEDGE, DINT = 1 and an interrupt occurs. DINTEDGE = 1 means rising edge, and 0 means falling edge. If the specified DIO line is in output mode, then writing to that line's output register with the correct transition will trigger the interrupt. When DINTCLR command is issued, the edge detect circuit will reset to be ready for the next edge. Setting DINTEN = 0 also resets the edge detect circuit, so that when DINTEN is set to 1 the circuit is ready for the first edge.

When register bit FINTEN = 1, a falling edge on DAC\_FAULT# will generate an interrupt and set register bit FINT = 1. The interrupt request is cleared, and FINT = 0, by writing a 1 to command bit FINTCLR or generating a reset. The interrupt routine is responsible for clearing the fault condition on the AD5755 to cause the fault pin to reset to 1.

# 7. A/D Circuit

## 7.1. A/D Input Ranges and Resolution

Jasper uses a 16-bit A/D converter. This means that the analog input voltage can be measured to the precision of a 16-bit binary number. The maximum value of a 16-bit binary number is 216 - 1, so the full range of numerical values that user can get from Jasper input channel is 0 - 65535.

The smallest change in input voltage that can be detected is 1/(2<sup>16</sup>), or 1/65536, of the full-scale input range. This smallest change results in an increase or decrease of one in the A/D code and is referred to as one Least Significant Bit (1 LSB).

## 7.2. Unipolar and Bipolar Inputs

Jasper can measure both unipolar (positive only) and bipolar (positive and negative) analog voltages. The fullscale input voltage range depends on the Gain, Range, and Polarity bit settings in the Analog Configuration register (Base+11). In front of the A/D converter is a programmable gain amplifier that multiplies the input signal before it reaches the A/D. This gain circuit has the effect of scaling the input voltage range to match the A/D converter for better resolution. In general, the user should select the highest gain possible that will allow the A/D converter to read the full range of voltages over which the input signals varies. If the gain is too high, the A/D converter clips at either the high end or low end, and the user will be unable to read the full range of voltages on the desired input signals.

## 7.3. Ranges and Resolutions

The table below lists the full-scale input range for each valid analog input configuration. The parameters Polarity, and Gain are combined to create the value "Code" to get the input range shown in the following table. These registers are made available on the Base+4 address. A total of nine different input ranges are possible. The range programming codes 4, 5, 6, and 7 are invalid and that range codes 9–11 are equivalent to range codes 0–2.

| Polarity | Range | Gain | Code | Input Range | Resolution (1 LSB) |

|----------|-------|------|------|-------------|--------------------|

| Bipolar  | 5V    | 1    | 0    | 5V          | 153mV              |

| Bipolar  | 5V    | 2    | 1    | 2.5V        | 76mV               |

| Bipolar  | 5V    | 4    | 2    | 1.25V       | 38mV               |

| Unipolar | 5V    | 1    | 4    |             | Invalid Setting    |

| Unipolar | 5V    | 2    | 5    |             | Invalid Setting    |

| Unipolar | 5V    | 4    | 6    |             | Invalid Setting    |

| Unipolar | 5V    | 8    | 7    |             | Invalid Setting    |

| Bipolar  | 10V   | 1    | 8    | 10V         | 305mV              |

| Bipolar  | 10V   | 2    | 9    | 5V          | 153mV              |

| Bipolar  | 10V   | 4    | 10   | 2.5V        | 76mV               |

| Bipolar  | 10V   | 8    | 11   | 1.25V       | 38mV               |

| Unipolar | 10V   | 1    | 12   | 0-10V       | 153mV              |

| Unipolar | 10V   | 2    | 13   | 0-5V        | 76mV               |

| Unipolar | 10V   | 4    | 14   | 0-2.5V      | 38mV               |

## 7.3.1. Conversion Formulas

The 16-bit value returned by the A/D converter is always a two's complement number ranging from -32768 to 32767, regardless of the input range. This is because the input range of the A/D is fixed at  $\pm$ 10V. The input signal is actually magnified and shifted to match this range before it reaches the A/D. For example, for an input range of 0–10V, the signal is first shifted down by 5V to  $\pm$ 5V and then amplified by two to become  $\pm$ 10V. Therefore, two different formulas are needed to convert the A/D value back to a voltage, one for bipolar ranges, and one for unipolar ranges.

To convert the A/D value to the corresponding input voltage, use the following formulas, depending on bipolar or unipolar mode of operation.

#### 7.3.1.1. Conversion Formula for Bipolar Input Ranges

#### Input voltage = A/D code / 32768 \* Full-scale input range

Example:

```

Given, Input range is \pm 5V and A/D code is 17761.

```

Therefore,

Input voltage = 17761 / 32768 \* 5V = 2.710V.

For a bipolar input range,

1 LSB = 1/32768 \* Full-scale voltage.

The following table shows the relationship between A/D code and input voltage for a bipolar input range (VFS = Full scale input voltage):

| Input Voltage Symbolic Formula | Input Voltage for ±5V Range                               |

|--------------------------------|-----------------------------------------------------------|

| -V <sub>FS</sub>               | -5.0000V                                                  |

| -V <sub>FS</sub> + 1 LSB       | -4.9998V                                                  |

|                                |                                                           |

| -1 LSB                         | -0.00015V                                                 |

| 0                              | 0.0000V                                                   |

| +1 LSB                         | 0.00015V                                                  |

|                                |                                                           |

| V <sub>FS</sub> - 1 LSB        | 4.9998V                                                   |

|                                | -V <sub>FS</sub> + 1 LSB<br><br>-1 LSB<br>0<br>+1 LSB<br> |

#### 7.3.1.2. Conversion Formula for Unipolar Input Ranges

Input voltage = (A/D code + 32768) / 65536 \* Full-scale input range

Example:

Given, Input range is 0–10V and A/D code is 17761.

Therefore,

Input voltage = (17761 + 32768) / 65536 \* 10V = 7.7103V.

For a unipolar input range, 1 LSB = 1/65536 \* Full-scale voltage.

The table on the following illustrates the relationship between A/D code and input voltage for a unipolar input range (VFS = Full scale input voltage).

| A/D Code | Input Voltage Symbolic<br>Formula | Input Voltage for<br>0-5V Range |

|----------|-----------------------------------|---------------------------------|

| -32768   | 0V                                | 0.0000V                         |

| -32767   | 1 LSB (V <sub>FS</sub> / 65536)   | 0.153 mV                        |

|          |                                   |                                 |

| -1       | V <sub>FS</sub> / 2 - 1 LSB       | 4.99985V                        |

| 0        | V <sub>FS</sub> / 2               | 5.0000V                         |

| 1        | V <sub>FS</sub> / 2 + 1 LSB       | 5.00015V                        |

|          |                                   |                                 |

| 32767    | V <sub>FS</sub> - 1 LSB           | 9.9998V                         |

## 7.4. A/D Sampling Methods

#### 7.4.1. FIFO Description

Jasper uses a 2048-sample FIFO (First In First Out) memory buffer to manage A/D conversion data. The FIFO is used to store A/D data between the time it is generated by the A/D converter and the time it is read by the user program. In enhanced mode, the entire 2048-sample FIFO is available. In normal mode only 1024 samples are available. The FIFO may be enabled and disabled under software control.

In single-conversion mode, the FIFO features are not generally needed so FIFO use should not be selected (although the FIFO is actually being used). Each A/D sample is stored in the FIFO. When the software reads the data, it reads it out of the FIFO. In low-speed sampling, each time a conversion occurs, the program reads the data, so there is always a one-to-one correspondence between sampling and reading. Thus, the FIFO contents never exceed one sample.

For high-speed sampling or interrupt operation, the FIFO significantly reduces the amount of software overhead in responding to A/D conversions. Using the FIFO also reduces the interrupt rate on the bus because it enables the program to read multiple samples at a time. In addition, the FIFO is required for sampling rates in excess of the maximum interrupt rate possible on the bus. Generally, the fastest sustainable interrupt rate on the ISA bus running DOS is around 40,000 per second. Since Jasper can sample up to 250,000 times per second, the FIFO is needed to reduce the interrupt rate at high speeds. When the interrupt routine runs, it reads multiple samples from the FIFO. The interrupt rate is equal to the sample rate divided by the number of samples read each interrupt. On jasper, this number is programmable using the FIFO Threshold register (Base+6). The usual value is 1/2 the maximum FIFO depth, or 1024 samples. Therefore, the maximum interrupt rate for Jasper is reduced to 996 per second, which is easily sustainable on any popular operating system.

**Note:** If both scan and FIFO operations are enabled, the interrupt occurs at the programmed FIFO threshold and the interrupt routine reads the indicated number or samples and then exits. This happens even if the number of samples is not an integral number of scans. For example, if the user has a scan size of 10 and a FIFO threshold of 256, the first time the interrupt routine runs, it reads 256 samples, consisting of 25 full scans of all 10 channels followed by 6 samples from the next scan. The next time the interrupt routine runs, it reads the next 256 samples, consisting of the remaining 4 samples from the last scan it started to read, the next 25 full scans of 10 samples, and the first 2 samples of the next scan. (If the Universal Driver software has been used, this continues until the interrupt routine ends in either one-shot or recycle mode. In one-shot mode, the last time the interrupt routine runs it reads the entire contents of the FIFO, making all data available.)

## 7.4.2. Scan Sampling

A scan is defined as a quick burst of samples of multiple consecutive channels. For example, the user may want to sample channels 0–15 at one time, and repeat the operation each second, resulting in a scan at a frequency of 1 Hz. Each time the A/D clock occurs (software command, timer, or external trigger), all 16 channels are sampled in high-speed succession. There is a short delay of 4–20 microseconds between each sample in the scan. Since each clock pulse causes all channels to be sampled, the effective sampling rate for each channel is the same as the programmed rate, and the total sampling rate is the programmed sampling rate times the number of channels in the scan range.

Scan sampling is independent of FIFO operation and can be enabled independently.

#### 7.4.3. Sequential Sampling

In sequential sampling, each clock pulse results in a single A/D conversion on the current channel. If the channel range is set to a single channel (high channel = low channel), each conversion is performed on the same input channel. If the channel range is set to more than one channel (high channel > low channel), then the channel counter increments to the next channel in the range, and the next conversion is performed on that channel. When a conversion is performed on the high channel, the channel counter resets to the low channel for the next conversion. The intervals between all samples are equal. Since each clock pulse results in only one channel being sampled, the effective sampling rate is the programmed sampling rate divided by the number of channels in the channel range.

#### 7.4.4. Sampling Methods

There are several different A/D sampling modes available on DSC SabreCom-JSP User Manual. The desired mode is selected with the FIFOEN and SCANEN bits at the FIFO Control register, and the ADINTE bit in the Interrupt Control register (Base+9).

**Note**: If interrupts are not enabled, the FIFO should not be enabled. FIFO storage is only useful when interrupts are used. Otherwise, the FIFO has no effect.

All of these features may be selected as arguments to function calls in the driver software. The control register details are provided for completeness and for programmers not using the driver.

| SCANEN | FIFOEN | ADINTE | Mode                                                                                                                                                                                                                                                                                                                                                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No     | No     | No     | Single<br>Conversions                                                                                                                                                                                                                                                                                                                                                                  | The most basic sampling method. Used for low-speed<br>sampling (typically up to about 100 Hz) under software<br>control where a precise rate is not required, or under external<br>control where the rate is slow. Consists of either one channel<br>or multiple channels sampled one at a time.                                                                                                                      |

| Yes    | No     | No     | Scan<br>Conversions                                                                                                                                                                                                                                                                                                                                                                    | Used to sample a group of consecutively numbered channels<br>in rapid succession, under software or external control. The<br>time between samples in a scan is programmable between 5<br>to 20 microseconds, while the time between scans depends<br>on the software or external trigger and may be very short or<br>very long, but is usually less than about 100 Hz (above this<br>rate use interrupt scans below). |

| No     | No     | Yes    | Interrupt<br>Single<br>Conversion,<br>Low Speed<br>Used for controlled-rate sampling of single channels or<br>multiple channels in round-robin fashion, where the<br>frequency of sampling must be precise but is relatively<br>(<100Hz). The sampling clock comes from the on-boar<br>counter/timer or from an external signal. The interval<br>between all A/D samples is identical. |                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Yes    | No     | Yes    | Interrupt<br>Scans, Low<br>Speed                                                                                                                                                                                                                                                                                                                                                       | Used for controlled-rate sampling a group of channels in low-<br>speed mode (<500Hz per channel). Each sampling event<br>consists of a group of channels sampled in rapid succession.<br>The time between scans is determined by the sample rate.                                                                                                                                                                     |

| SCANEN | FIFOEN | ADINTE | Mode                                             | Description                                                                                                                                                                                                                                                                                      |

|--------|--------|--------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No     | Yes    | Yes    | Interrupt<br>Single<br>Conversion,<br>High Speed | Intended for medium- to high-speed operation<br>(recommended above about 500 Hz). Can support sampling<br>rates up to the board's maximum of 250,000 Hz. May also be<br>used at slower rates if desired. The sampling clock comes<br>from the on-board counter/timer or from an external signal. |

| Yes    | Yes    | Yes    | Interrupt<br>Scan<br>Conversions                 | Used for high-speed sampling of a group of channels where<br>the scan rate is high. The sampling clock comes from the on-<br>board counter/timer or from an external signal.                                                                                                                     |

# 8. D/A Circuit

Jasper utilizes the Analog Devices AD5755 D/A converter for all analog output functions. The AD5755 provides 4 16-bit DACs with high accuracy, low drift, programmable voltage and current output ranges, and digital calibration. Up to 4 of these devices may be installed on the board depending on the model. A precision, low-drift 5V voltage reference circuit provides the basis for the overall accuracy of the analog outputs.

The AD5755 contains an integrated digital calibration circuit consisting of a multiplier and adder. Each time data is written to a DAC, it undergoes a multiplication / addition operation, and the result is then transferred to the DAC channel. This operation takes about 5 microseconds to complete. Thus, each write to a DAC channel results in a 5 us delay before the output begins to update to the new value. The total settling time for one channel consists of the settling time for the DAC plus this calibration time.

## 8.1. Ranges and Resolutions

#### 8.1.1. Ranges

The chips provide voltage outputs in multiple output ranges. Each channel on each chip can be set to a different output range. Each channel has a voltage output pin and a ground return pin. The application wiring must connect to the voltage output pin or the current output pin, as needed.

A D/A converter converts a number, or output code, into an output voltage or current that is proportional to the number. The output range is the range of possible output values, from the smallest (lowest) value up to the highest (largest) value. The difference between the highest and lowest output value is called the span. For a +/- 5V output range, the span is 10V.

Jasper uses straight binary coding for all output values; the range of output codes is 0-65535. The theoretical top value, 65536, requires 17 bits to be represented in binary form, which is unachievable in a 16-bit value. Therefore, the top value of each output range is unavailable, and instead the maximum output value is 1 LSB less than the top value. Because the lowest output code is always 0, which is represented in binary form, the bottom value of each range is always equal to the exact nominal value of the range (within tolerance of the accuracy).

For example: In Jasper the 16-bit DAC can generate output voltages with the precision of a 16-bit binary number. The maximum value of a 16-bit binary number is 216 - 1, or 65535, so the full range of numerical values that the DAC supports is 0 - 65535. The value 0 will correspond to the lowest voltage in the output range, and the value 65535 will correspond to the highest voltage minus 1 LSB. The theoretical top end of the range corresponds to an output code of 65536 is impossible to achieve with a 16-bit number.

#### 8.1.2. Resolution